参考文献

原理图设计

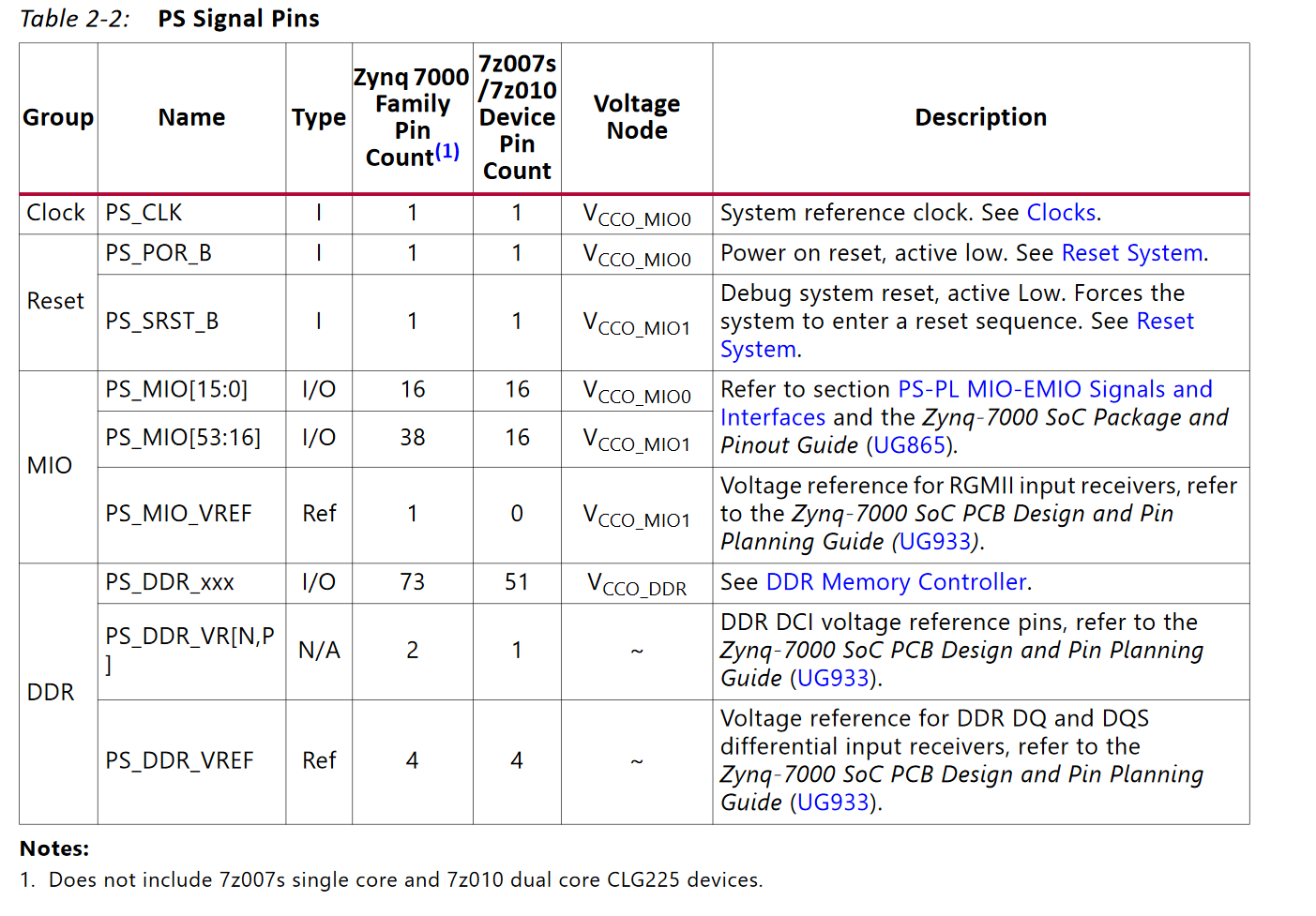

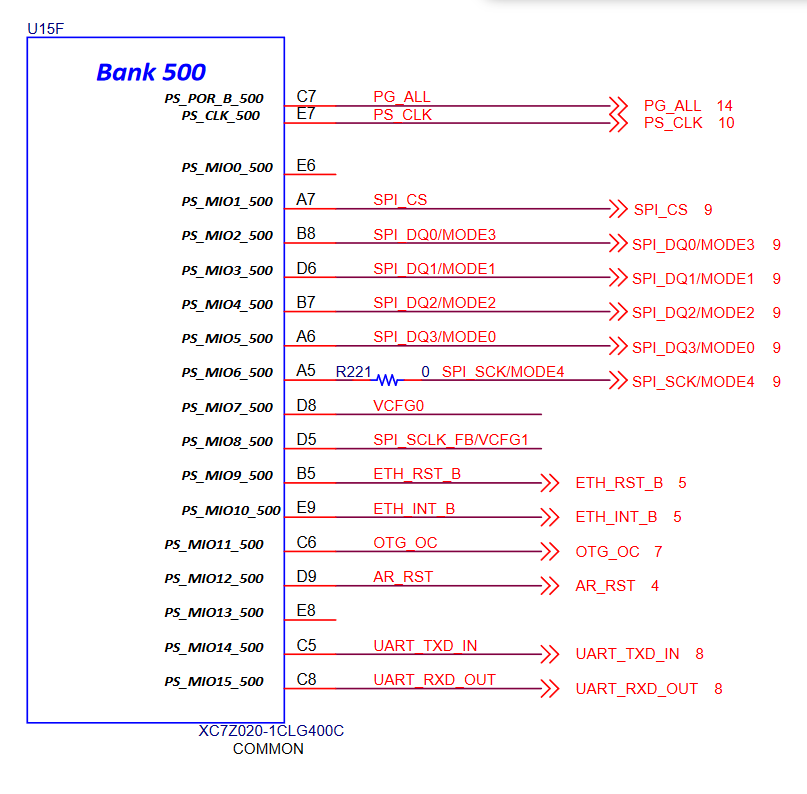

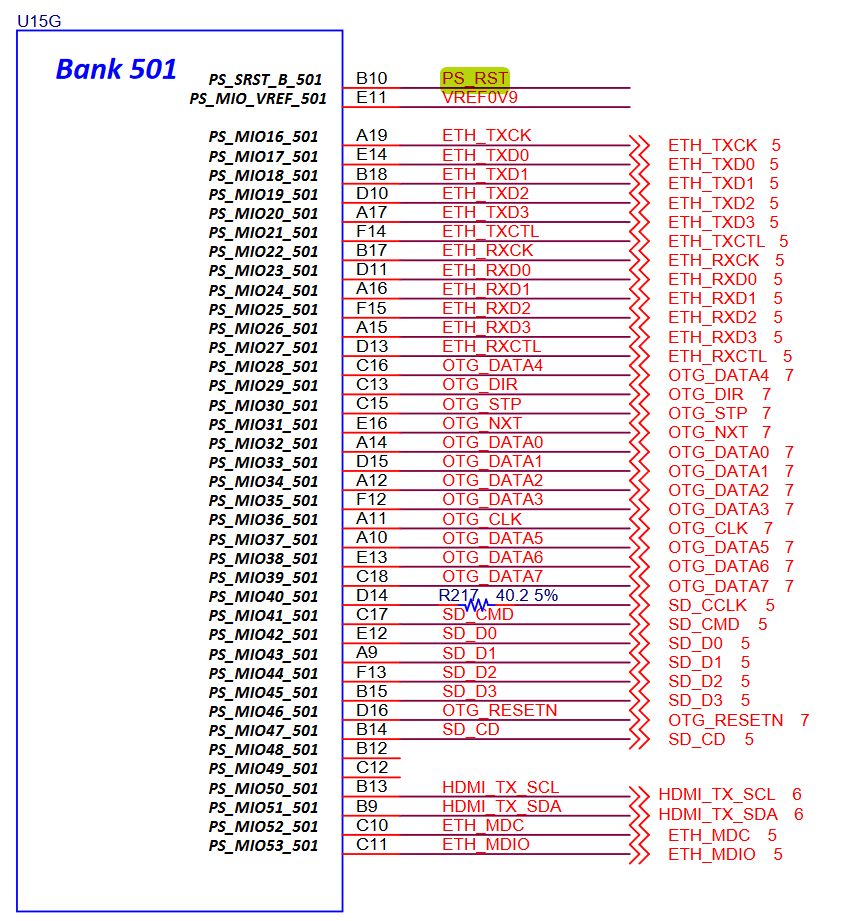

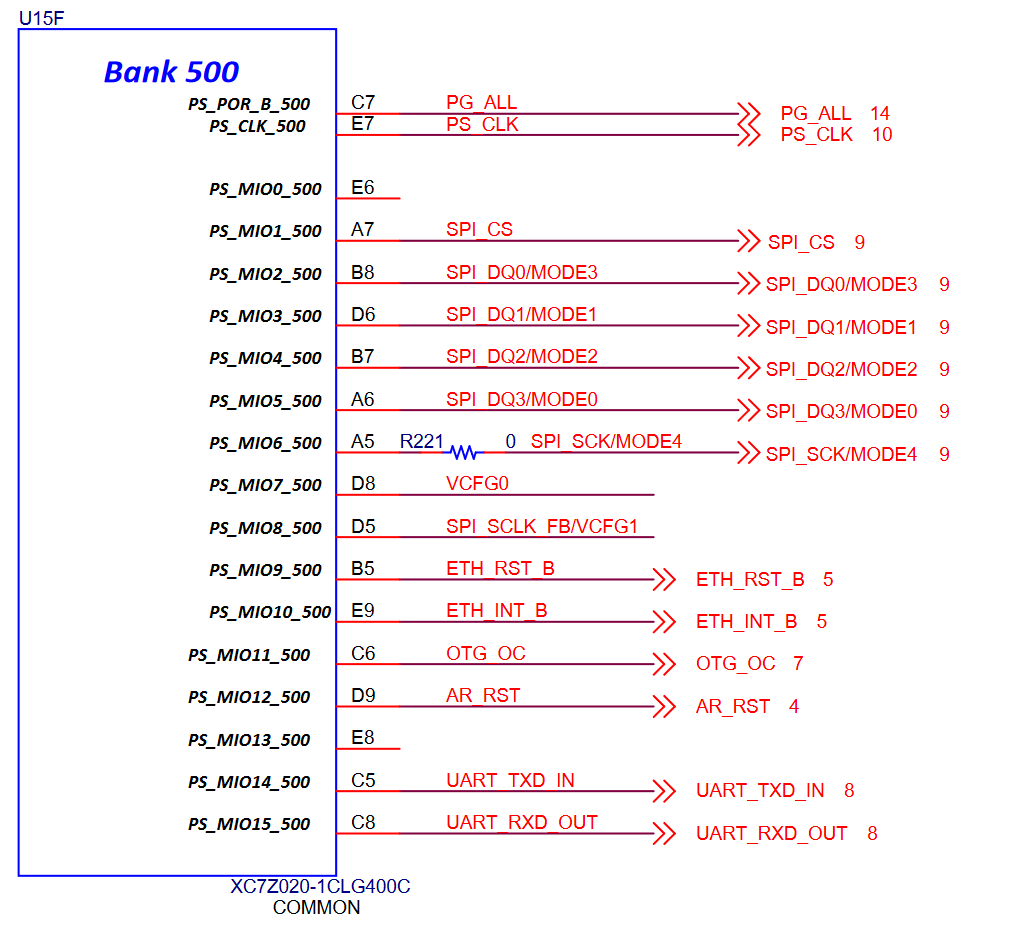

PS部分

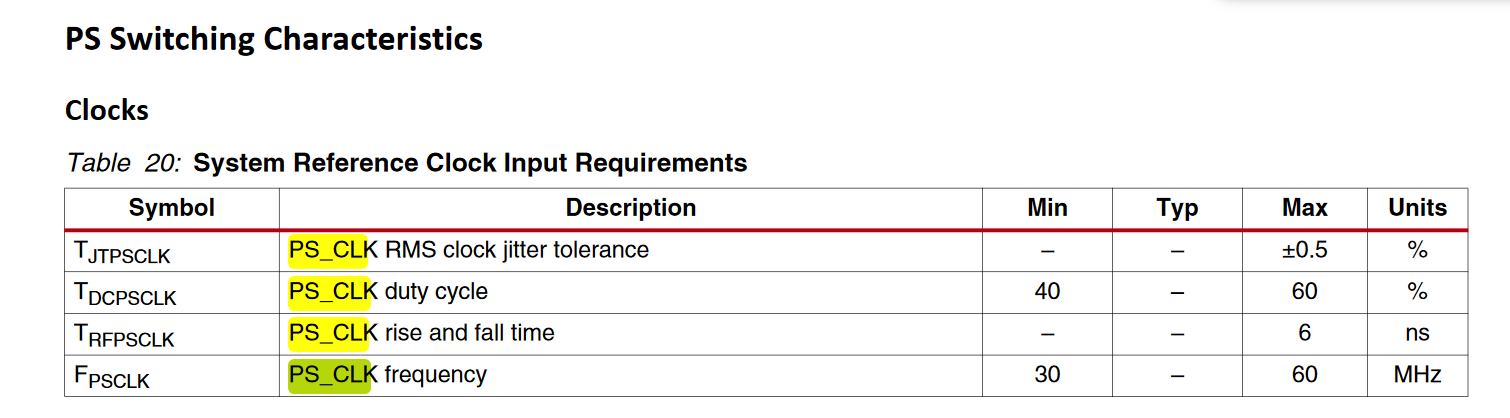

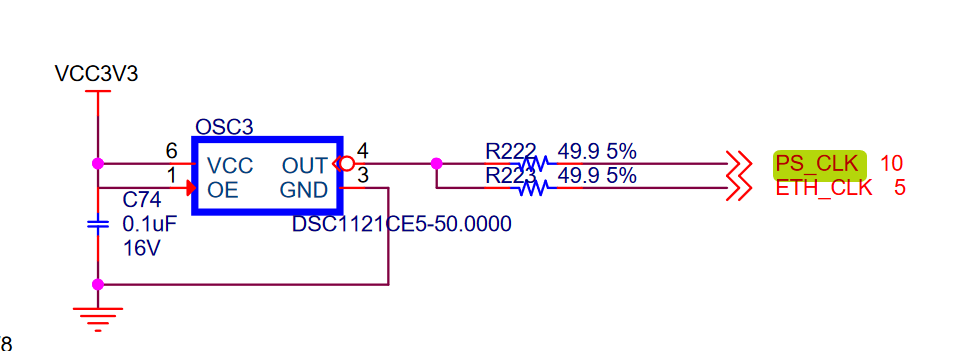

时钟

看了下PYNQ,用的50Mhz,不过频率30到六十都行麻

这两个复位比较有意思 PYNQ上,PS_POR_B最后给到了PG_ALL,而PS_SRST_B给到了真正的外部复位上。

PYNQ上,PS_POR_B最后给到了PG_ALL,而PS_SRST_B给到了真正的外部复位上。

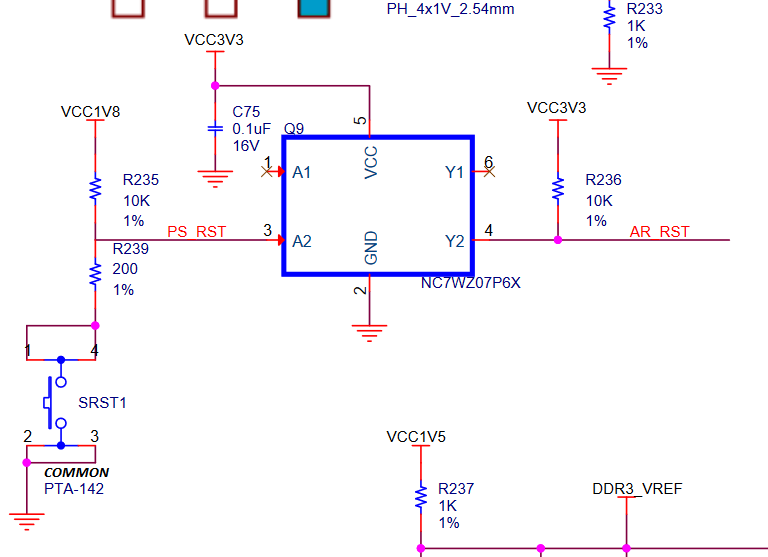

不过这个AR_RST没看懂啊,NC7WZ07P6X是个缓冲器,AR_RST一端给到了排针的外部接口上,但他又接回PS上去了,他的RESET用的是1.8V电压,因为bank501是1.8电压域,但是为啥又接到3.3的电压域的PS引脚上去了?不懂

需要注意的是,两个RESET分属不同的电压域,PYNQ上,PS_POR_B的电压域是3.3V,而PS_SRST_B的电压域是1.8V

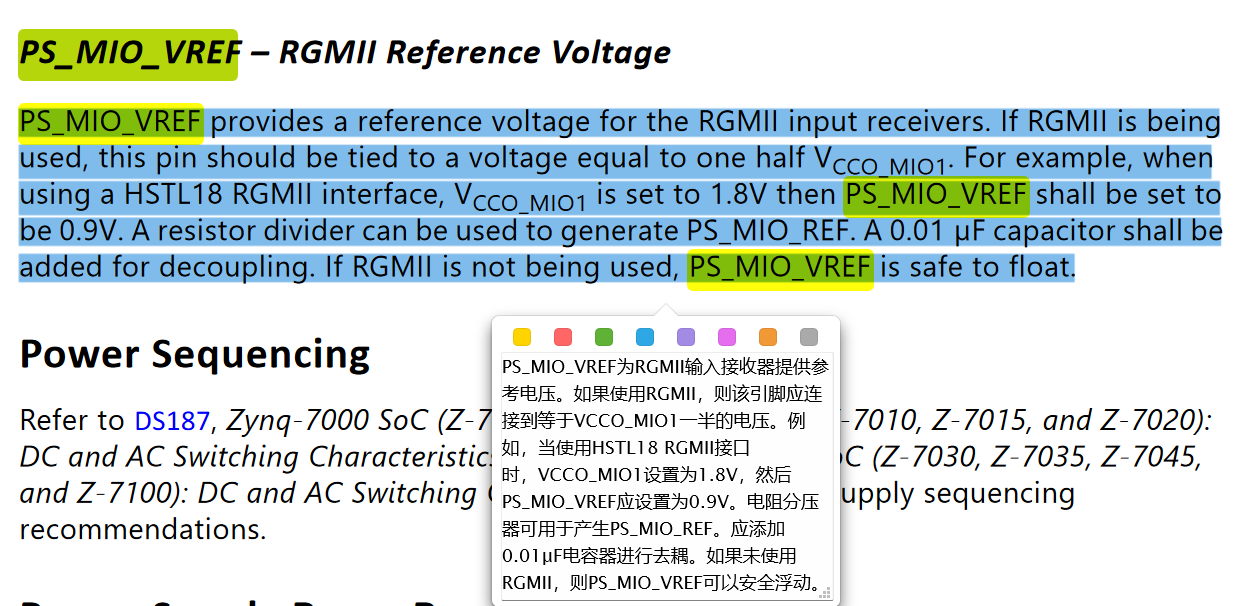

最后一个PS_MIO_VREF,看图

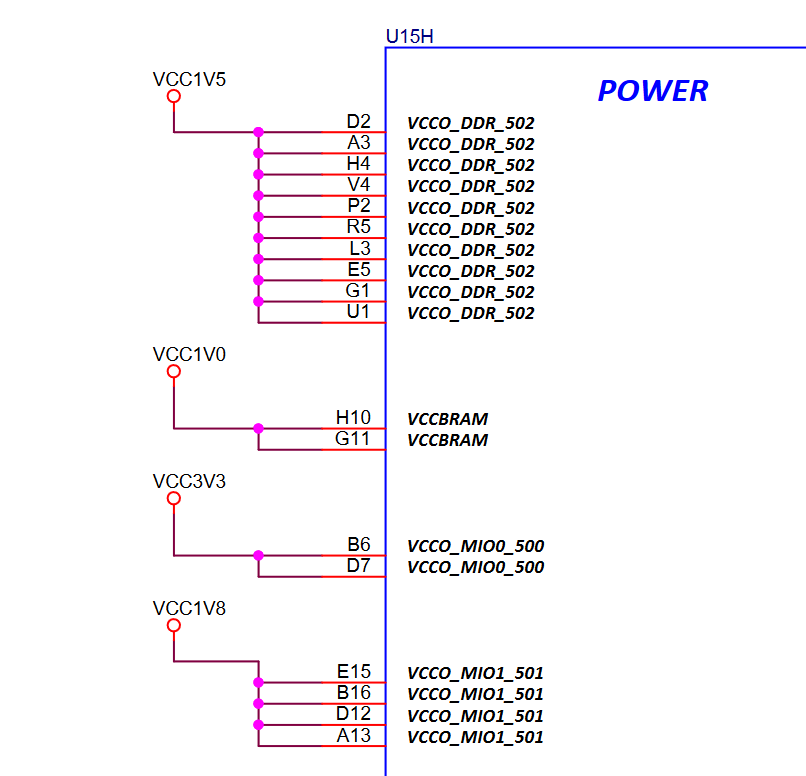

接下来是Vivado分配引脚Vivado的PS引脚分配不知道咋导出来,直接抄PYNQ

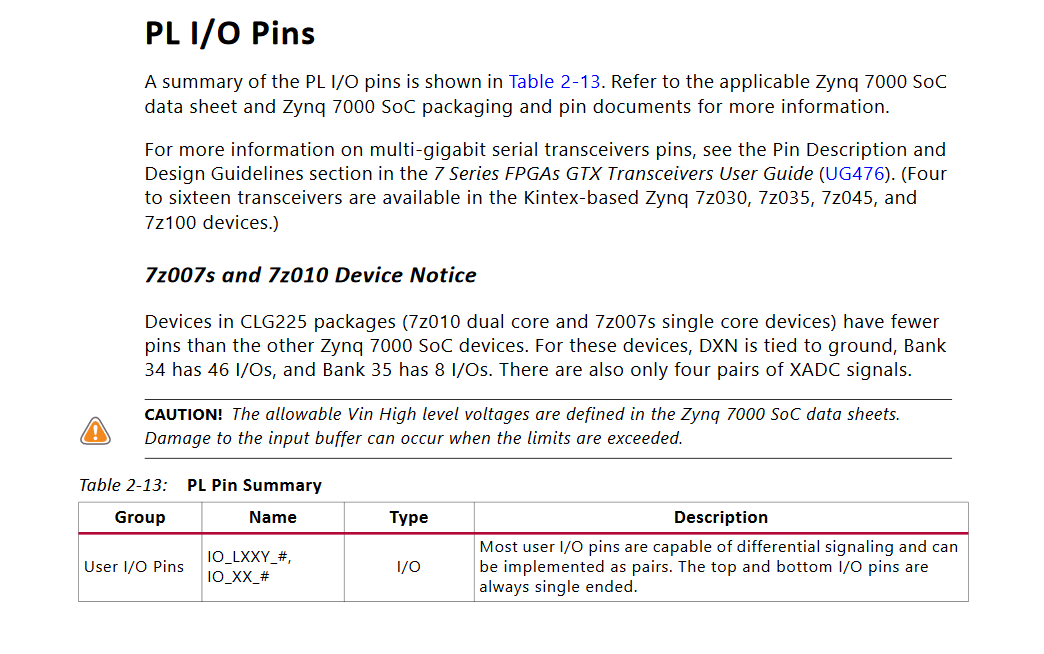

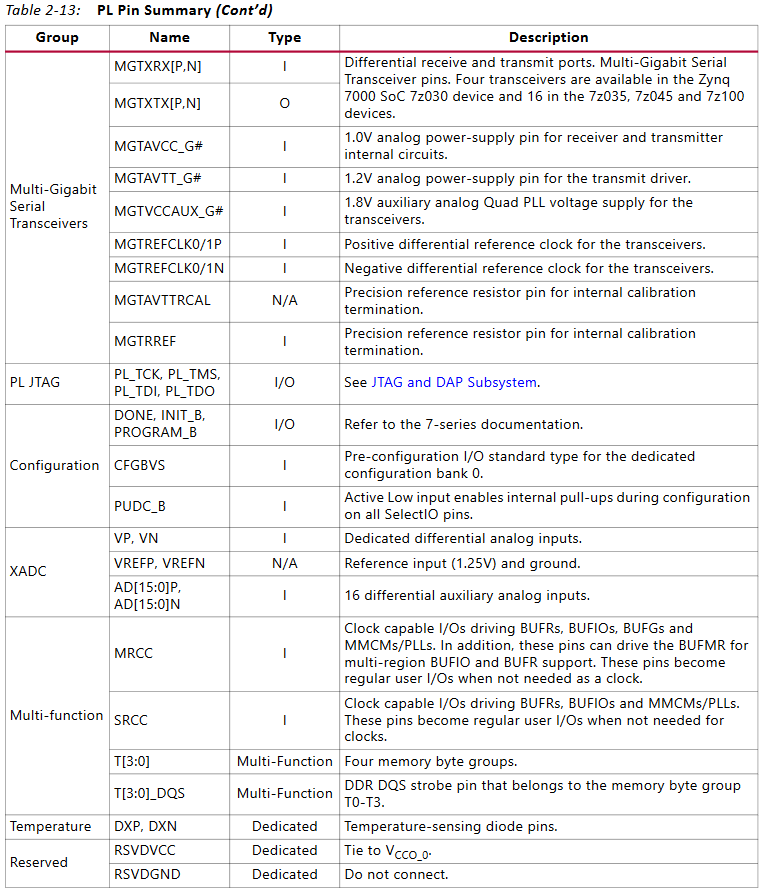

PL部分

引脚说明

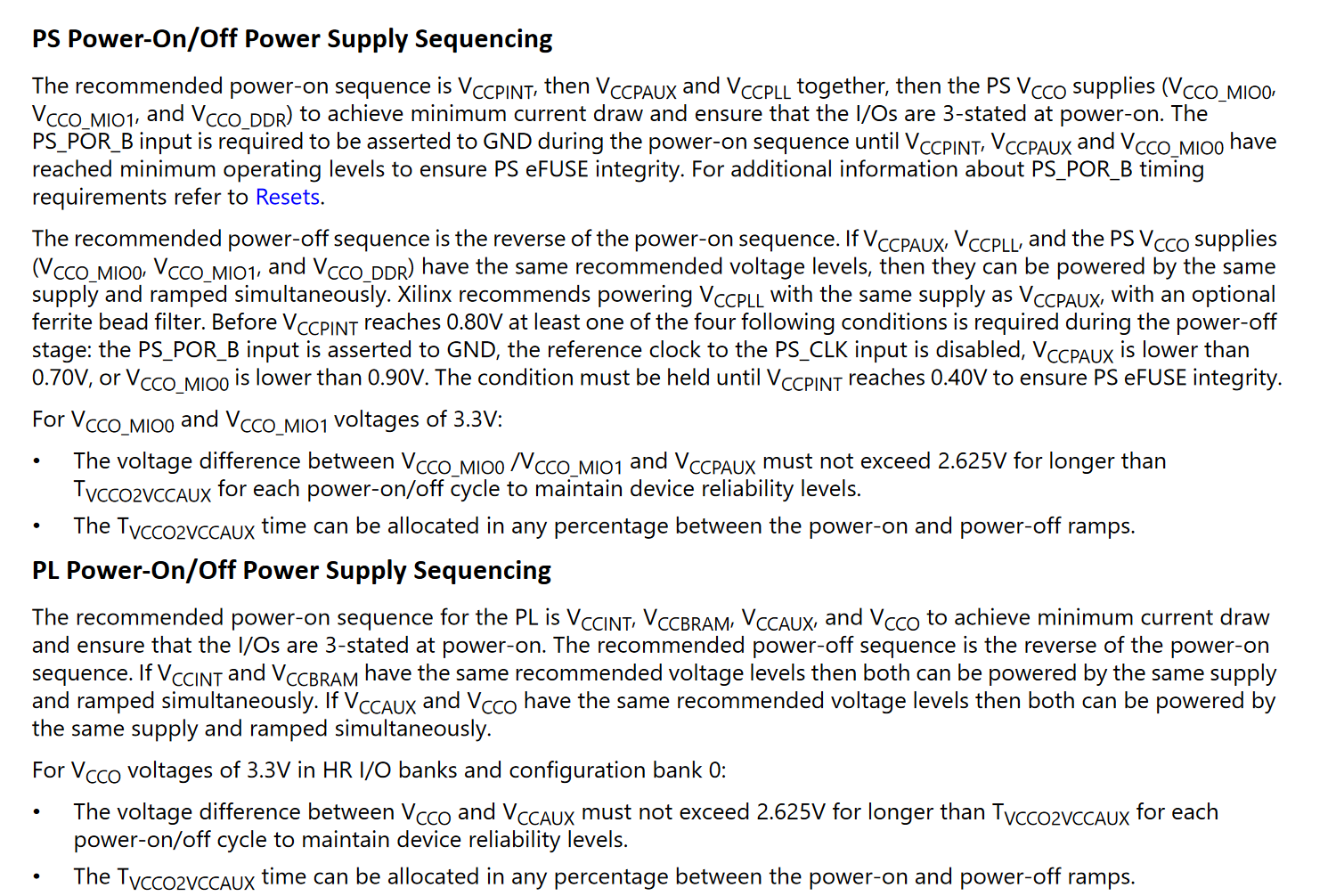

上电时序

PS和PL的电源是完全分离的,不必考虑相互耦合。